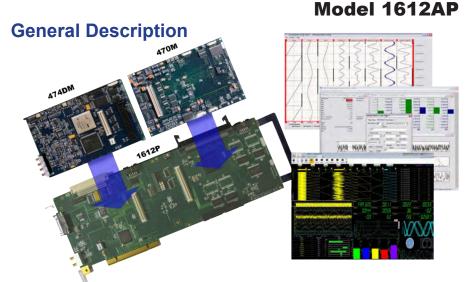

# **New Advanced PCI Telemetry Decom Processing Cardset**

## **Features:**

- Third Generation 0-72 Mbps PCI "all-in-one" Telemetry Processor Card (streaming, burst and packet enabled)

- OS agnostic card embedded dynamic "soft-decom" processors

- Reliable, WIN 10 STIG compliant 1 to 8 stream system configurations

- State-of-the-art modular Bit Sync, Advanced CH 4 Class 2 Decom, IRIG Time & Sim in a single slot

- Upgraded companion Model 1615AP

PDSP 6MS / sec EU processor module

- Decom data-driven low latency recording & playback

- Acroamatics GUI Telemetry System Software (ATSS) included - Lifetime Support!

- Integrated IADS & Dewesoft client display/analysis and Turn-key ILIAD compatibility

- Compliance with IRIG 106 Chpt 4 (class 1 & 2), CVSD, Chpt 8, Chpt 9, (TMATS), Chpt 10, TMoIP compatible

- NASA CCSDS & packet TM decommutation, TMoIP compatible

- IRIG Ch 10 format file export

- O-64 Mbps Programmable

PCM Simulator & PCM Stream

Reconstructor

IRIG Chapter 4/5/8/9/10 CVSD **TMATS**

The recently updated Model 1612AP card embedded telemetry decom and multi-function processing module features the highest data rate and processing speeds in the industry, yet retains 100% "drop-in" compatibility with legacy Acroamatics PCI TDP products and systems.

Utilizing the latest in FPGA component technology to deliver both low power (1/3 that of the preceding generation) and improved reliability, the new 1612AP features real-time card embedded stored program processing technology, providing multiple software program driven sub-frame decommutators - each with multiple onboard data and conditional stored memory program locations. Though the 1612AP PCI decom operates wholly independently of its host Windows chassis administrative OS, it is designed to allow use of standard Windows driven PCI bus and system processes to independently record data to disk, drive Windows display processes, and share data over network connections - making it a very effective stand alone all-in-one telemetry processing device.

As part of an integrated multi-stream / low latency real-time telemetry processing solution, up to eight independent 1612AP cards operate in conjunction (via dedicated 64-bit I-Bus) with Acroamatics companion 1615AP PCI PDSP module. The PDSP delivers 100% Windows application independent card level EU derived, and user defined processing and output data formatting capabilities.

## **Real Time PCM Frame Sync/Decommutator**

## Model 1612AP Card Embedded Programmable Low Latency Frame Sync/Decom/Data Output Formatter

| PCM Input                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sources                         | To four program selectable decom inputs supported, TTL NRZ-L Data and 0° Clock.<br>When configured with optional Model 474DM bit sync a fifth program selectable internal bit sync input path is provided.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Impedance<br>Bit Rate           | 50 Ohm input impedance, TTL compatible.<br>From 0 to 72 Mbps, burst, jam, and streaming mode compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Polarity                        | Programmable, automatic polarity correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Word Length<br>Word Orientation | Programmable, 1 to 32 bit word length for each input.<br>Programmable, MSB/LSB orientation for each input word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Parity                          | Selectable leading, trailing, or no parity checking for each word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Synchronization                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Mainframe Sync                  | Provides for programmable sync pattern and mask, complement pattern recognition, and variable length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                 | frame decommutation. The pattern may be up to 64 bits in length.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Subframe Sync                   | Six independent synchronizers are capable of decommutating sub-frames within subframes. Subframes synchronize to fixed recycle patterns, complement frame sync patterns, and various ID patterns. Both recycle and ID patterns may be assembled from multiple word locations. Recycle patterns may be up to 32 bits long.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ID Sync                         | Two types of ID synchronization are supported: JAM patterns of arbitrary values, and incrementing or decrementing frame counters with limit checking. ID sync words may be up to 16 bits in length.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Sync Strategy                   | Programmable Search-Check-Lock sync strategy, bit error tolerance, and bit slip window provide reliable frame synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Asynchronous Formats            | Subframe synchronizer may be programmed to decommutate embedded formats having unique frame sync patterns and format structures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Format Switching                | <sup>1</sup> 6 testable flags store the results of select input stream bit and word comparisons to control real-time format switching Frame Sync / Decom format switching is loss-less and immediate. Multiple card resident micro-coded decom processing programs are stored in local decom memory in support of such conditional format switching events.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Outputs                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                 | Data is available to the host computers PCI bus as memory-mapped frame buffers, Current Value Table (CVT), or as a data stream selectably transferred by PCI bus DMA. Data is 32 bits with programmable MSB/<br>LSB output word justification, sign extension, or zero insertion for LSB output. Acroamatics Telemetry System<br>Software (ATSS) suite provides a host of Windows compatible (XP and Windows 7 compatible) which support<br>user decom set-up, mission set-up management, and a host of real-time data display, alarming, recording,<br>discrete/analog, and networked data I/O processes and local operator status display, and remote system<br>management and data operations support.                                                                                                                                                                                                                                                                                                                                |

| I-Buss Data Output              | When used in a system configured with a 1605P or new 1615AP PDSP PCI level advanced telemetry processing modules, the Model 1612AP uses a 64 bit parallel "I-bus" low latency inter-card connection that processes messages containing thirty two bits of data, twelve bits of fine time (microseconds), two bits of status, and 17 bits of data identification. I-bus data can be formatted in either MSB or LSB justified form. LS-justified data can also be sign extended. I-bus decom data is transmitted to the 1605P or new 1615AP PDSP card resident distribution & algorithmic data processor. The 1605P/1615AP is capable of from up merging data from any of up to eight 1612P cards in a system, to form the desired EU processing data and formatted data output products in support of real-time analog (DAC) output, raw or processed data recording, real-time display, and networked data communications processes. Decom and bit sync data quality status words are generated for downstream data validation, as well. |

| 2 Serial PCM Outputs            | Two programmably controlled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **PCM Simulator/Encoder**

## Model 1612AP Card Embedded User Programmable 1 bps - 64 Mbps PCM Simulator/Encoder

## PCM Programmable PCM Format Simulator/Encoder Functions

| •                            |                                                                                                            |      |

|------------------------------|------------------------------------------------------------------------------------------------------------|------|

| Format Storage               | Stores two complete, selectable PCM formats. Performs asynchronous frame insertion and format switching    | ing  |

| Subframe Capability          | Generates up to three subframes within mainframe. Generates subframe within subframe                       |      |

| Frame Length                 | Up to 65,536 words for the mainframe and 16,384 per subframe                                               |      |

| Data Sources                 | 256k unique user programmable static word registers                                                        |      |

|                              | Two complete user-defined onboard stream simulation data memories. Two 16-bit module up/down count         | ters |

|                              | Two 16-bit external inputs. One 16-bit pseudo-random number generator.                                     |      |

|                              | One 16-bit program counter                                                                                 |      |

| Word Length                  | Programmable for each data source: static data words 1 to 32 bits; all others 1 to 16 bits                 |      |

| Word Orientation             | Program selectable: MSB/LSB for each data word                                                             |      |

| Parity Generation            | Program selectable: leading, trailing, or no parity for each data word                                     |      |

| <b>Dynamic Data Memories</b> | 2 unique, user-defined 16kB RAM's. Presettable to ramp, sine, triangle and squarewave functions or         |      |

|                              | user-defined input. Selectable data type: 1's complement, 2's complement, signed magnitude, offset binary. |      |

|                              | Programmable time base.                                                                                    |      |

|                              |                                                                                                            |      |

ACROAMATICS

## **PCM Outputs**

| Bit Rate     | Program selectable: 1Hz to 64MHz, tunable to 0.1% of programmed rate                  |

|--------------|---------------------------------------------------------------------------------------|

| Clock        | 0° clock                                                                              |

| Data         | NRZ-L                                                                                 |

| Output Codes | Program selectable: NRZ-L/M/S, Biø-L/M/S, DBiø-M/S, DM-M/S, MDM-M/S, RNRZ 11/15/17/23 |

| PCM Output   | TTL compatible NRZ-L data and 0° clock                                                |

## **Bit Synchronizer**

Model 474DM (Option - companion mezzanine module to Model 1612AP)

#### **PCM Signal Inputs**

| Two each analog baseband user selectable PCM inputs - #1 single ended, #2 RS-422 |

|----------------------------------------------------------------------------------|

| Greater than 60dB at 20MHz                                                       |

| Program selectable: Hi-Z/Lo-Z. Single Ended: 4kΩ/75Ω, Differential: $10$ kΩ/150Ω |

| Single Ended: 0.2-20V P-P, Differential: 0.2-10V P-P                             |

| 20V max Hi-Z                                                                     |

| Program selectable: NRZ-L/M/S, Biø-L/M/S, DBiø-M/S, DM-M/S, MDM-M/S, RZ          |

| Program selectable: RNRZ 9/11/15/17/23, forward/reverse                          |

|                                                                                  |

#### Synchronization

| Bit Rate Range<br>Capture Range<br>Loop Bandwidth<br>Sync Threshold<br>Sync Maintenance<br>Sync Acquisition<br>Sync Retention<br>Bit Error Rate | 8bps - 72MHz NRZL, 8 bps - 40 Mbps Biø Codes<br>3 times the programmed loopwidth, typical<br>0.1% to 3.2%, program selectable in 0.1% increments<br>0dB for NRZ-L and Biø-L codes<br>(LW=0.1%) –2dB NRZ-L and Biø-L codes<br>(LW=1.6%, SNR > 12dB) Typically less than 32 bit periods<br>(LW=0.1%, SNR > 3dB) Retains sync through > 1028 + consecutive dropouts, all modes<br>(LW=0.1%) to within 0.25 to 0.50 dB of ideal bit error rate performance curves, absolute (not average) in all<br>modes |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## **IRIG Time Code Reader/Generator**

Model 470M (Option - companion mezzanine module to Model 1612AP, one per system)

## IRIG Time Code Reader/Generator/Translator

| 0.5 to 20 Vpp, Single-ended                   |

|-----------------------------------------------|

| 12K Ohms minimum                              |

| Translates IRIG G, A, B, & NASA-36            |

| 125 Hz to 400,000 Hz                          |

| 2:1 through 5:1.                              |

| Program selectable, Invert or Normal Polarity |

| Time Base 40MHz crystal oscillator            |

|                                               |

## **Operational**

| Generate Mode           | Time is generated from the onboard crystal oscillator and is pre-settable from the Host.                                                            |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Translate Mode          | Time is read from an external source.                                                                                                               |

| Translate Carrier Mode  | 5                                                                                                                                                   |

|                         | This mode enables the system to translate time as the input carrier rate varies during playback of an analog recording                              |

| Translate Failsafe Mode | The internal timing is phase-locked to the input carrier. In the event of time dropout, the translator continues generating time without interrupt. |

| Frame Bypass            | Automatic frame bypass compares previous time frame with current one, and Time Accumulator updates when they agree                                  |

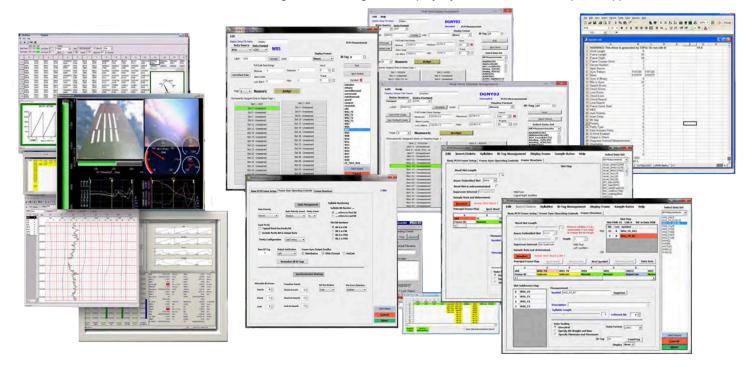

## System Software ATSS/TMATS/IADS/ILIAD

## Acroamatics Telemetry Software Suite (ATSS)

| Processing Environment | Real-time, Windows OS independent processing. Dynamic "Change on the Fly" capable conditional format switching. Embedded PCI Module based "soft decom" on functionally dedicated, card based micro-coded                                                                                                         |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | processors                                                                                                                                                                                                                                                                                                       |

| Standards Compliant    | IRIG Chapter 4, 5, 8, 9 and 10 compatible TMATS Import, NASA CCSDS, integral IADS Data Services, LabVIEWS and Matlab.                                                                                                                                                                                            |

| Data Display Types     | Scalable multi display/page, 32 pages -Horizontal and vertical strip chart, tabular,bargraph, annunciator, controls / meters, each with dynamic limit checking, alarming, scalable, parameter and E/U annotation.                                                                                                |

| Data Recording         | The ATSS Data Recording Client provides local operator control of the 4022 CTS record function, and can operate as a standalone application or in conjunction with ATSS software managed real-time telemetry processing operations.                                                                              |

| Networking             | The Model 4022 CTS supports both networked system set-up and operation admin and real-time data communications. ATSS Remote operations software (\$225 option) provides remote users all functions offered to the local user, including data recording, data display, system status and set-up GUI applications. |

## Options

Tunable Bit SynchronizerThe Model 474DM 8 Hz to 40 MHz Advanced Digital Bit Sync Mezzanine Module may be ordered with or<br/>added to the 1612AP.IRIG Time CodeOne Model 470M IRIG Time Reader/Generator / PCM Sim Mezzanine is required per system for IRIG time

#### One Model 470M IRIG Time Reader/Generator / PCM Sim Mezzanine is required per system for IRIG time sync / generate.

## Physical

| i nysicai            |                                                                                    |

|----------------------|------------------------------------------------------------------------------------|

| Format               | Standard PCI: full length single slot                                              |

| Cooling Requirements | 30 Linear FPM                                                                      |

| Power Requirements   | +3.3VDC at 3.0 Amps, (including optional mezzanine bit sync and / or time modules) |

| Dimensions           | 4.20" (10.67cm) H x 12.5" (31.75cm) W x .55" (1.4cm) D                             |

| Temperature          | Operating: 0° to +40° C, Non-Operating: -40° to +86° C                             |

| Relative Humidity    | Up to 90% non-condensing                                                           |

| Shock                | Operating: 6G, Non-Operating: 50G                                                  |

| Vibration Operating  | 0.5G, 5 to 2000Hz, Non-Operating: 1.2G, 5 to 500Hz                                 |

|                      |                                                                                    |

7230 Hollister Avenue, Suite 100, Goleta, CA 93117 Phone: 805-967-9909 Fax: 805-967-8375 © 2017 Acroamatics. Inc.